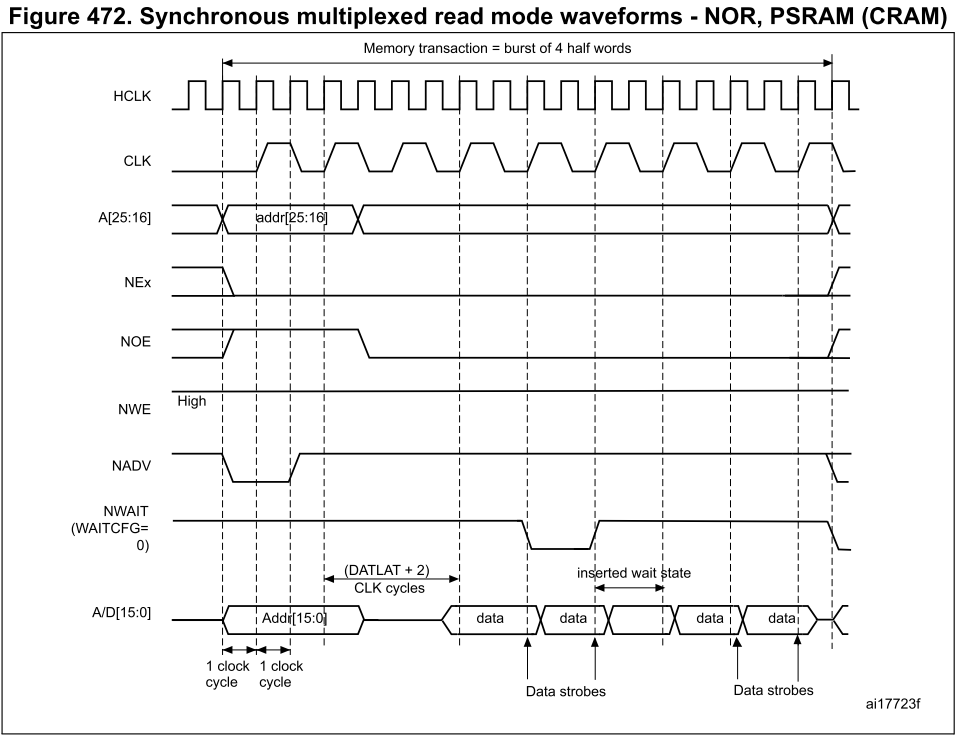

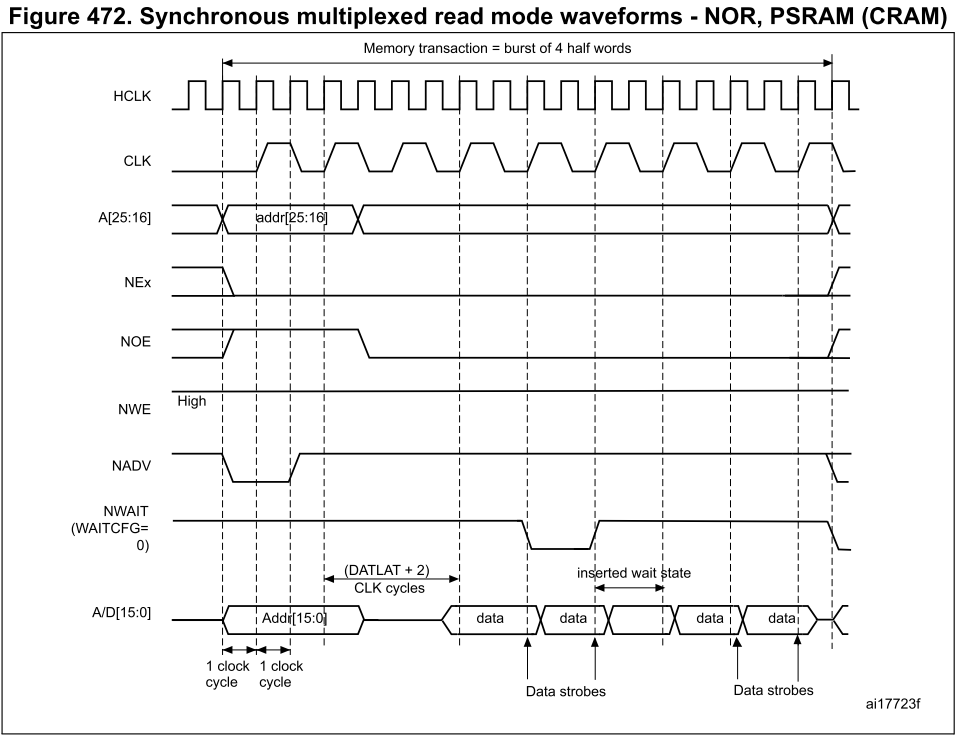

当前设计STM32F429需要从前级FPGA内部实现的FIFO接口中读取一帧(2048X16bit)数据。由于目前FSMC总线上已经挂上了SDRAM,所以为了节约STM32管脚,我想通过FSMC总线读取FIFO。由于FSMC没有针对FIFO接口的模式,所以在比较各种模式后,我想采用修改后的PSRAM接口的同步复用模式。

具体做法:地址线A[25:16]不用连到FPGA,FPGA内部判断NEx有效且NADV为数据有效时,将NOE信号取反后连到FIFO的RD管脚,数据线D[15:0]全部连到FIFO的出口数据管脚。实现时数据线和NOE可能需要FPGA内部调整一下对齐,这个问题不大。

对于这个方案我有两个问题:

1. 这个方案是否可行?有没有什么问题需要注意?

2. 如果可行的话,读取数据的burst长度最大可以设置为多少?(希望最好是2048个数据一个burst就可以读完,如果可以的话)。

具体做法:地址线A[25:16]不用连到FPGA,FPGA内部判断NEx有效且NADV为数据有效时,将NOE信号取反后连到FIFO的RD管脚,数据线D[15:0]全部连到FIFO的出口数据管脚。实现时数据线和NOE可能需要FPGA内部调整一下对齐,这个问题不大。

对于这个方案我有两个问题:

1. 这个方案是否可行?有没有什么问题需要注意?

2. 如果可行的话,读取数据的burst长度最大可以设置为多少?(希望最好是2048个数据一个burst就可以读完,如果可以的话)。

友情提示: 此问题已得到解决,问题已经关闭,关闭后问题禁止继续编辑,回答。

硬件上是可以这么区分,但是软件呢。两者的时序完全不同,初始化的代码也不一样,难道要用一次sdram就调用一下sdram初始化代码,用一次fpga就调用一次psram的初始化代码吗?

cpu读fpga中的fifo我之前做过两种,一种是TI的upp接口,是同步接口,upp的时钟可以直接接异步fifo的时钟,速率快。另外一种就是fsmc,用的是异步模式,fpga端涉及到异步时钟域的同步问题,速率比较慢。两种模式都可以,看应用的需求

一周热门 更多>