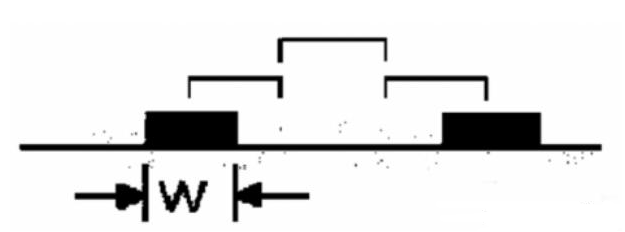

何为3W原则?

3W原则就是两条走线的间距是线宽的3倍,如下图1所示。为了减少传输线之间的串扰,在PCB设计时应保证足够宽的线间距,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则,当然,如果不走线允许,10W间距都是没由问题的。

备注:3W原则一般针对高速信号线长距离走线,并不是强制所有PCB走线都要满足此原则。

3W原则

为何要遵循3W原则?

既然都说PCB走线要遵循3W原则,那么为何是3W?而不是4W、3.5W或者2W?带着这个问题,小编下面就给大家详细讲解下为何PCB走线要遵循3W原则?

多说大家可能也记不清楚,那么就直接用ADS简单仿真分析下,带大家看看PCB设计为何要遵循3W原则!

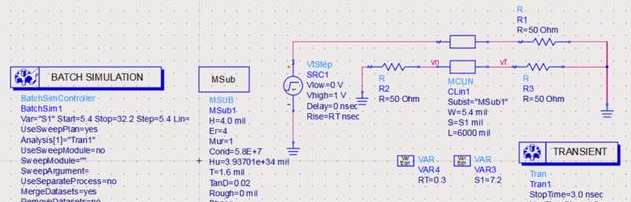

我们首先在ADS原理图上添加相关仿真控件、50Ohm电阻和微带线模型等,这里我们以线间距S作为变量,在信号源、层叠结构、传输线线宽等参数确定之后,分别仿真远端串扰(vn)和近端串扰(vf),如下图2所示。

ADS 3W 仿真模型(L=6000mil)

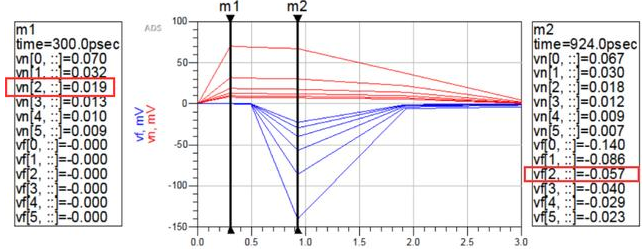

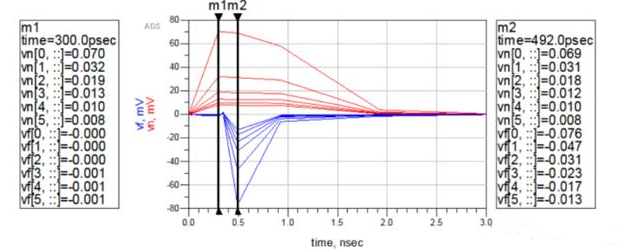

如下图3为仿真结果,在上升时间为0.3ns时,激励源的幅值为1V,当传输线之间的间距为3W时,即近端串扰vn[2,::]和远端串扰vf[2,::]分别为19mV和57mV,相当于激励源的1.9%和5.7%。 也即是说,当传输线之间的间距为3W时,传输线的近端串扰和远端串扰分别只剩下源信号的1.9%和5.7%。

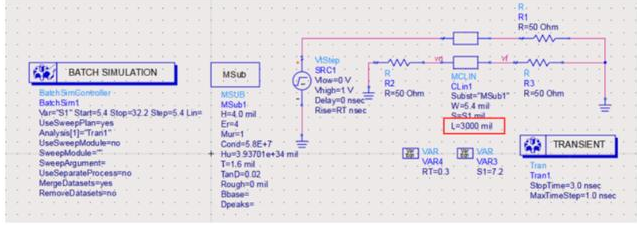

值得注意的是,这里远端串扰相对来说稍微有点大,是因为传输线的耦合长度为6000mil,这个长度比较长,我们把传输线耦合长度降低为3000mil时,再仿真一次,如下图4所示。

传输线耦合长度降低为3000mil仿真结果

根据仿真结果得知,此时近端串扰vn[2,::]和远端串扰vf[2,::]分别为19mV和31mV,可以看出,远端串扰降低了将近一半,此时相当于激励源的3.1%,基本都能满足一般设计的要求。这也是为什么很多设计都设定传输线与传输线的间距至少要保证3W线宽的原因!

总结

3W原则虽然易记,但要强调一点,这个原则成立是有先前条件的。从串扰成因的物理意义考量,要有效防止串扰,该间距与叠层高度、导线线宽相关。

3W原则是一种防止串扰的一种方法,该方法仅作为一种参考,并作为理解如何防止串扰的一种启发。实际PCB设计中,3W原则并不能完全满足避免串扰的要求,有时候还要进行屏蔽地线包地等处理,以防止串扰的发生。