2017FPGA基本任务计数器仿真实验

题目来源

http://blog.csdn.net/DUWT_LAB/article/details/70207490

目录

计数器仿真实验 1 内容

电路结构RTL设计图

Quartus扫描生成的电路RTL图

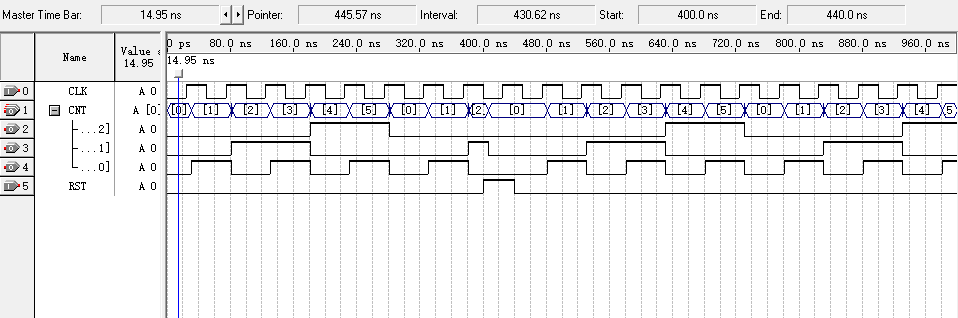

电路的波形仿真截图

HDL代码

module counter(CLK,RST,CNT);

input CLK,RST;

output reg[2:0] CNT;

always @(posedge CLK or posedge RST)

begin

if(RST)

CNT<=3'b0;

else

if(CNT<5)

CNT<=CNT+3'b001;

else

CNT<=3'b0;

end

endmodule

计数器仿真实验 2内容

电路结构RTL设计图

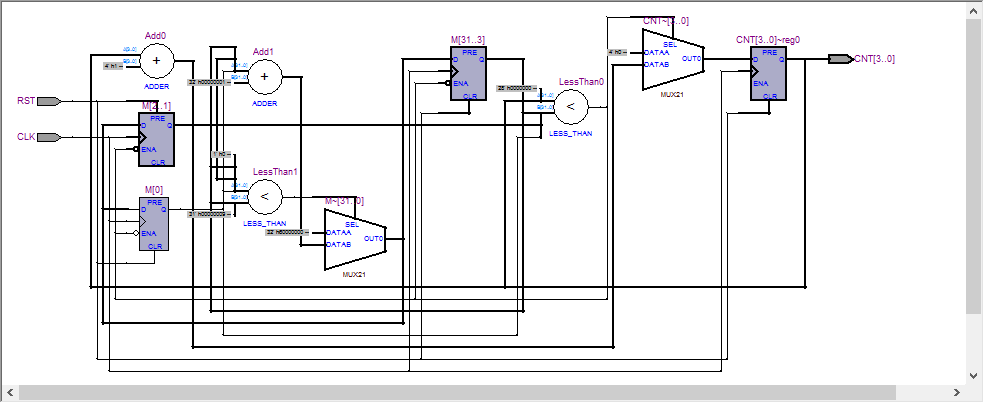

Quartus扫描生成的电路RTL图

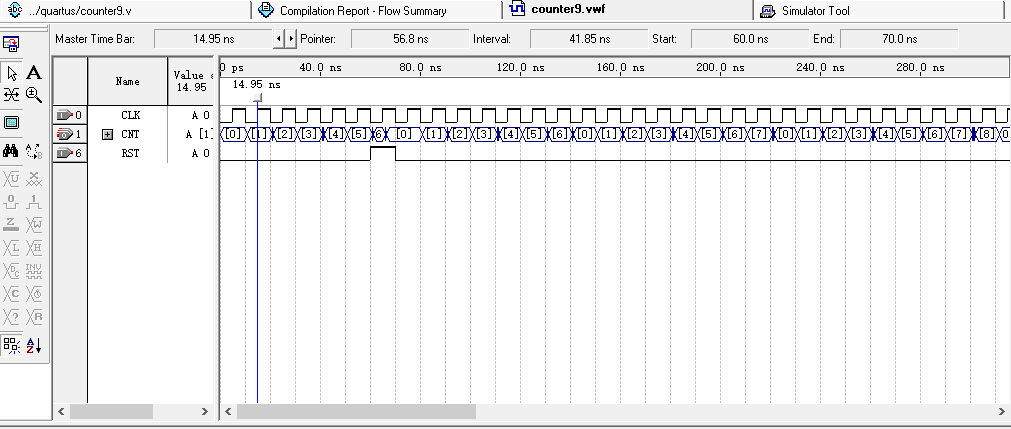

电路的波形仿真截图

HDL代码

module counter9(CLK,RST,CNT);

input CLK,RST;

output reg[3:0] CNT;

integer M=6;

always @(posedge CLK or posedge RST)

begin

if(RST)

begin

CNT<=4'b0;

M=6;

end

else

if(CNTbegin

CNT<=CNT+4'b0001;

end

else

begin

CNT<=4'b0;

if(M<9)

M<=M+1;

else

M<=6;

end

end

endmodule